**MAY** 2013

www.edn-europe.com Issue 5

## europe

SoC interfacing of strain-gauge based sensors Page 13 Test & measurement technology goes embedded Page 24 10 software tips for hardware engineers Page 30

### 16 SoC FPGAs combine performance and flexibility

Embedded-system architectures built on a combination of MCUs and FPGAs offer the kind of adaptability increasingly required to support changing demand for greater functionality across diverse applications. by Michael Parker, Altera Corp

#### 13 A system-on-chip approach to interfacing strain-gauge based sensors

The strain gauge is a useful sensor in industrial applications, given that its principle of operation is understood and its various forms of errors are taken into account. Mixed-signal programmable ICs offer a method of interfacing that increases performance and provides the required accuracy.

by Umanath R Kamath, Cypress Semiconductor

#### 24 Test & measurement technology goes embedded

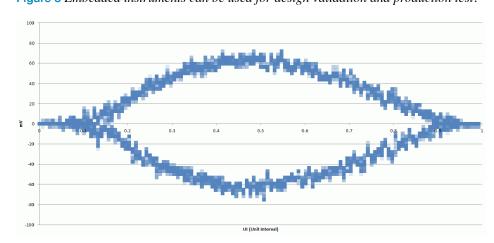

The high rate of innovation occurring in microcontrollers and FPGAs enables opportunities for creation of multifunctional electronics, that are more intelligent, more suitable for networking, re-configurable, and compact in size; test, for development and production, must keep pace. by Thomas Wenzel, Goepel electronic

### 30 10 C language tips for hardware engineers

It can be common for a hardware designer to write code to test that hardware is working. These 10 tips for C—still the language of choice—may help the designer avoid basic mistakes that can lead to bugs and maintenance nightmares. by Jacob Beningo, Beningo Engineering

#### **DEPARTMENTS & COLUMNS**

#### 5 EDN.comment

Hit the switch

#### 12 Signal Integrity

Measuring nothing

#### 14 Teardown

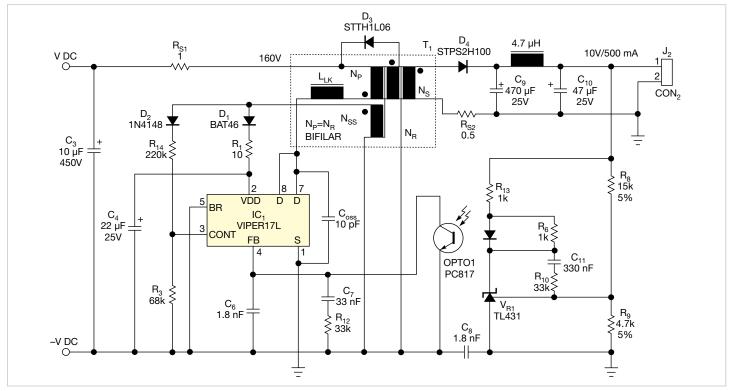

LED light shrinks size and cost with nonisolated driver by Margery Conner, designing with leds.com

#### 42 Tales from the Cube

Decoupling caps are where it's at

#### 50 Product Roundup

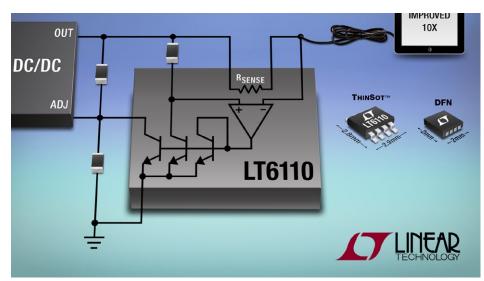

Cable drop compensator for power rails: TI's Stellaris MCUs are now Tiva

#### **DESIGNIDEAS**

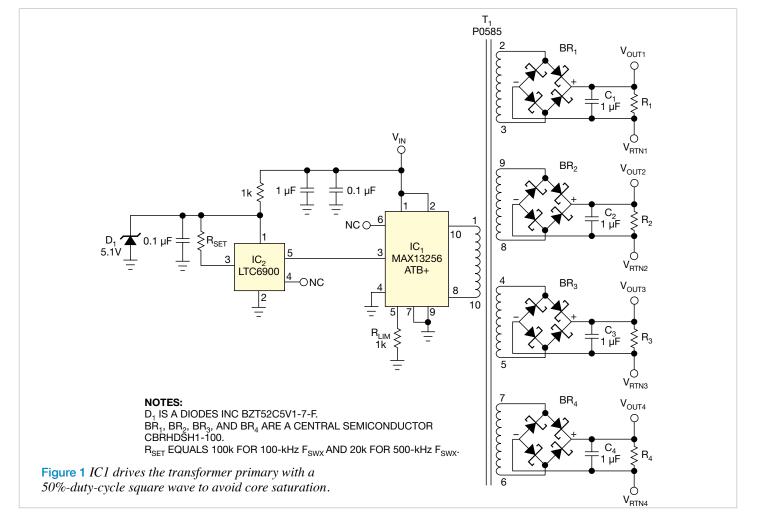

- 33 Recover the leakage energy of a flyback transformer

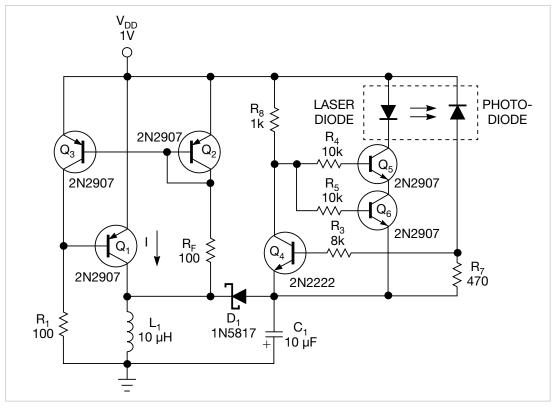

- 35 Double the protection of a laser driver using a 1V power supply

- 36 Gate-drive transformer eases multi-output, isolated dc/dc converter designs

### pulse

- 6 xCORE industrial multicore microcontrollers gain analogue functions

- 6 Single-chip touch control for Windows 8 tablets

- 8 Tek builds on Voltech acquisition with power analyser launch

- 8 USB 2.0 interface, coax physical layer on MOST150 network chip

- Multi-channel, multi-standard signals to6 GHz from R&S vector generator

- 11 Single-chip digital radio receivers for consumer electronics

- 11 Battery monitoring technology adds precision for lead-acid chemistry

### Automotive COOLiRIGBT™ Gen 1

#### Ultra-fast Switching, Rugged 600V High Frequency IGBTs

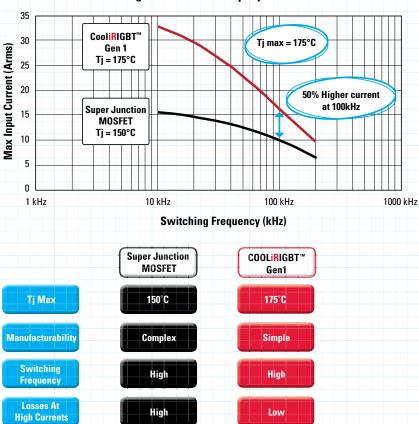

#### CooliRIGBT™ offers 50% higher current than super junction MOSFETs

COOLIRIGBT™ Gen 1 are designed to be used in a wide range of fast switching applications for electric (EV) and hybrid electric vehicles (HEV) including on-board DC-DC converters, and battery chargers.

#### Features:

- Switching frequencies up to 200kHz

- 600V rated devices with a short circuit rating of > 5µs

- Low V<sub>CE(on)</sub>

- Positive V<sub>CE(on)</sub> temperature coefficient making the parts suitable for paralleling

- Square Reverse Bias Safe Operating Area

- Automotive qualified

- Tj max of 175ºC

- Rugged performance

- Designed specifically for automotive applications and manufactured to the OPPM initiative

For more information call +49 (0) 6102 884 311

or visit us at www.irf.com

**MAY** 2013

www.edn-europe.com Issue 5

## europe

#### **CONTACTS**

#### **PUBLISHER André Rousselot**

+32 27400053 andre.rousselot@eetimes.be

#### **EDITOR-IN-CHIEF Graham Prophet**

+44 7733 457432 edn-editor@eetimes.be

#### **Patrick Mannion**

european

business press

**Brand Director EDN Worldwide**

#### **CIRCULATION & FINANCE Luc Desimpel**

luc.desimpel@eetimes.be

#### **ADVERTISING PRODUCTION & REPRINTS**

Lvdia Giisegom

lydia.gijsegom@eetimes.be

#### **ART MANAGER**

**Jean-Paul Speliers**

#### **ACCOUNTING**

Ricardo Pinto Ferreira

#### **EUROPEAN BUSINESS PRESS SA**

7 Avenue Reine Astrid 1310 La Hulpe

Tel: +32 (0)2 740 00 50 Fax: +32 (0)2 740 00 59 www.electronics-eetimes.com VAT Registration: BE 461.357.437

RPM: Brussels

Company Number: 0461357437

© 2013 E.B.P. SA

#### EDN-EUROPE is published 11 times in 2013 by European Business Press SA, 7 Avenue Reine Astrid, 1310 La Hulpe, Belgium Tel: +32-2-740 00 50 Fax: +32-2-740 00 59 email: info@eetimes.be. VAT Registration: BE 461.357.437.

RPM: Nivelles. Volume 15, Issue 2 EE Times P 304128 It is is free to qualified engineers and managers involved in engineering decisions - see:

http://www.edn-europe.com/subscribe

Copyright 2013 by European Business Press SA.

All rights reserved. P 304128

#### SALES CONTACTS

#### **Europe**

#### **Daniel Cardon** France, Spain, Portugal

+33 688 27 06 35 cardon.d@gmail.com

#### **Nadia Liefsoens** Belaium

+32-11-224 397 n.liefsoens@fivemedia.be

#### **Nick Walker** UK, Ireland, Israel, The Netherlands

+44 (0) 1442 864191 nickjwalker@btinternet.com

#### Victoria & Norbert Hufmann Germany PLZ 0-3, 60-65, 8-9, Austria, Eastern Europe

+49 911 93 97 64 42 sales@hufmann.info

#### **Armin Wezel Germany PLZ 4-5**

+49 (0) 30 37445104 armin@eurokom-media.de

#### **Ralf Stegmann** Germany PLZ 66-69, 7

+49 7131 9234-0 r.stegmann@x-media.net

#### Monika Ailinger Switzerland

+41-41-850 4424 m.ailinger@marcomedia.ch

#### Ferruccio Silvera Italy

+39-02-284 6716 info@silvera.it

#### **Colm Barry & Jeff Draycott** Scandinavia

+46-40-41 41 78

jeff.draycott@womp-int.com colm.barry@telia.com

#### **USA & Canada**

#### Todd A. Bria West

+1 831 477 2075 tbria@globalmediasales.com

#### Jim Lees PA. NJ & NY

+1-610-626 0540 iim@leesmedia.com

#### **Steve Priessman** East. Midwest. **South Central** & Canada

+1-630-420 8744 steve@stevenpriessman.com

#### **Lesley Harmoning** East. Midwest. South Central & Canada

+1-218.686.6438 lesleyharmoning@gmail.com

#### **Asia**

#### Masaya Ishida Japan

+81-3-6824-9386 Mlshida@mx.itmedia.co.jp

#### **Bennie Hui Asian Sources Publications Hong Kong**

+852 2831 2775 bennie@globalsources.com

EDN Europe | MAY 2013 www.edn-europe.com

#### EDN.COMMENT

#### Hit the switch

There is a newspaper in the UK called the Daily Mail; and its companion title, the Mail on Sunday. Its political stance, I believe it's fair to say, is on the right of centre. Its style inclines to – let's not call it sensationalism – say, rather, to finding something alarming in almost any aspect of the news or, indeed, of modern life. Its readers – who appear to be very happy with the arrangement – are fed a constant diet of topics that they told they ought to be very angry about. Hold that thought, and please don't skip ahead in the text – there is a point to emerge.

We are all familiar with the concept of the smart grid. Many readers of this column will be concerned with developing products that will, in time, bring about the smart grid. The peak-to-average ratio (to borrow a metric from another sphere of technology altogether) of power generation is a serious constraint. The grid can, and does, impose step changes in demand that cannot possibly be met by the response time of (most) generating plant – conventional or thermal alike. Plant must therefore be run with capacity in reserve to meet all likely peaks, which is inefficient and, in an era in which "you can't be too green", less and less acceptable.

Long-established practices such as low-cost night-time tariffs were an attempt to smooth some of the longer-period peaks, but the smart grid will work on a shorter timescale. A proportion of the demand on the power grid feeds intermittent loads that are relatively insensitive to the detail of their duty cycles. Loads such as refrigeration, with long time-constants on the thermal side of the equation, may be indifferent to whether they are on or off for a few minutes in this hour, or in the next hour.

So the technologies with which we are all familiar – Zigbee, EnOcean or some other wireless mesh networking, or power line communications; a few extra lines of code in the appliance's microcontroller; solid-state switching of all loads; data concentrators, servers and some modelling of the network and its responses – all of these, as we know, will enable the grid to trim the peaks from the load, and better match base-load power generation to average demand. The consumer who gives the grid access to their smart appliances should expect to get a more favourable tariff in return. It will, or should, be a classic "win-win".

It takes, therefore, a particularly paranoid mindset, a fundamentalist distrust of all the works of any form of officialdom, to manufacture out of the first moves towards the smart grid, a page-one headline on a Sunday newspaper – and here I must resort to cliché and affirm that I am not making this up – that declares, "Big Brother to switch off your fridge". Or, you might conclude, considerable desperation in the search for a better leading story.

In reality, domestic appliances – even aggregated – probably won't make very much difference, but neither is their network connection inherently sinister. It's easy to mock this sort of thing and, as you can tell, have a good deal of fun in so doing. But it does remind us of the fact that, if those with an engineering mindset and training are not ready to speak up and add informed commentary, then the uninformed will have free rein. This, naturally, works both ways. If we challenge paranoia about power-company-controlled fridges, we should also be ready to point out the dangers inherent in other developments that conceal real but less understood hazards. Have you any candidates to suggest? Do you see any technology developments that the industry is currently working on where the possible hazards might outweigh the potential, or intended, benefits?

# PUISE

## xCORE industrial multicore microcontrollers gain analogue functions

XMOS has added a number of analogue functions to its multicore MCUs; integrated analogue functions will reduce component count, save power, and improve signal integrity, allowing you to combine analogue and digital interfacing, communications and deterministic control in a single device. xCORE-Analog is a range of 6, 8, 10, 12 and 16-core multicore microcontrollers that XMOS configured fordesigners of industrial products. With an integrated analogue-to-digital converter, power management circuitry and a range of timers, the xCORE-Analog or 'A-Series' devices will be used in a range of industrial applications such as interfaces, high-level sensors and actuators, PLCs, communications devices and motor controllers. Developers can use a level of multicore computation resource scaled to their exact requirements.

A-Series chips include up to eight channels of 12-bit, 1 Msample/sec A/D conversion; power-on reset, brown-out protection and watchdog facilities; integrated oscillator; deep-sleep memory; and integrated DC/

16A7C10 16A7C10 16A7C10 US1324 P6028.00 P6028.00

XMOS' multicore, deterministic MCUs now have analogue functions on-chip

DC converter. You can reduce external component-counts and implement designs using simple two-layer printed circuit boards. The devices' power management features enable low sleepmode power consumption of 100 µA. The introduction of the A-Series follows several recent announcements from XMOS in the industrial arena, including the addition of industrial Fieldbus capabilities; the launch of an industrial serial bus (IS-BUS) I/O card for the modular sliceKIT development system; and the announcement of a collaboration with Synapticon enabling smart motor control and service robotics applications. The A-Series is supplemented by the xSOFTip range of soft peripherals, which includes realtime Ethernet, USB and human-machine interface (HMI) functions.

As with the pure-logic XMOS products, a major claim for the A-Series is timing predictability; it also brings the extremely low latency and hardware-level responsiveness of xCORE multicore microcontrollers to developers working on any type of system that needs to interface with analogue signals. Like the

existing xCORE-General Purpose (L-Series) and xCORE-USB (U-Series) product ranges, the A-Series is configured and programmed via the xTIMEcomposer Studio development toolset, a C-based design environment that is timingaware, allowing you to interface with hundreds of different types of sensors at the front end, xCORE A-Series devices will be sampling in Q2 2013, with volume production expected in Q4. Pricing is from \$4.60 (25k+). XMOS; www.xmos.com or for distribution sources, www.xmos.com/contact/ distributors

## Single-chip touch control for Windows 8 tablets

Atmel has extended its maxTouch range of touch controller ICs with the T-series. With high volumes of touch products being marketed in smartphone/ handset and tablet formats, Atmel has optimised this product for that sector. The mXT2952T is, according to Rob Frizzell, Director Touch Product Marketing in Atmel, mXT2952T: the first ultra low-power, single chip, capacitive touch solution for Windows 8 certified 15.6-in. displays. This conforms to the Windows 8 specification of up to 15.6 inch - but you can control an larger touch screen under Linux or Android, Frizzell says. The series offers solutions for screens of 3 to 23 inches. The company has incorporated several of the features it has developed for existing Atmel touch products. You can use the maxStylus (on screens of up to 13.3 in.), an active stylus that interacts with the touch sensing matrix without the need for an extra sensor layer; the maxFusion SensorHub integrates motion and sensory controls; and the Xsense technology supports the use of flexible and "edgeless" - or frameless - displays. The maxTouch T uses dual mutual- and self-capacitance sensing, claimed to give the best performance in terms of power, noise immunity, glove-touch sensitivity, moisture-insensitivity and latency. It handles 2952 nodes, has a refresh rate of over 150 Hz, can track at over 60 inches per second, and track 10 touches at over 100 Hz with full noise avoidance. Latency is under 10 msec. You can use fine-line-metal (FLM) screen technology as well as ITO overlays, and a 32-bit AVR-derived microcontroller filters noise, computes multi-touch points, and eliminates false responses. The mXT2952T replaces a 3-chip set to achieve similar results, occupies a 5 x 10 mm package and could yield a functional outline of 6 mm wide by 80 mm long to fit within a typical portable product build. Frizzell estimates a cost reduction over the 3-chip solution of around 2x.

Atmel, www.atmel.com

## Ever wished for a better bench scope?

The new R&S®RTM: Turn on. Measure.

Easy handling, fast and reliable results — exactly what users expect from a bench oscilloscope. Rohde & Schwarz opens the door to a new world: Work with two screens on one display. Access all functions quickly. Analyze measurement results while others are still booting up. See signals where others just show noise. That's the R&S®RTM.

Ever wished there was an easier way? Ever wished for more reliable results? Ever wished you could do your job faster?

Then take a look. www.scope-of-the-art.com/ad/rtm-video

Trade In Program available until June 2013:

Save up to 40 % on a new scope now! www.scope-of-the-art.com/ad/trade-in

## Tek builds on Voltech acquisition with power analyser launch

Earlier this year Tektronix acquired the power-analyser product line and intellectual property, in that speciality, of Voltech. Now, bringing to market a project that was under way at Voltech, Tek has introduced the PA4000 Precision Multi-Phase Power Analyser, offering power electronics engineers high levels of measurement accuracy on real-world signals. A key piece of technology is the current shunt employed in the analyser, which is termed the Spiral Shunt: this design confers stability in measurements as it remains constant over load and temperature, including self-heating effects, in terms of the resistance it presents. This, Tek says, gives power electronics engineers stable, precise current measurements even on highly distorted power waveforms common in many applications. Tek presents the PA4000 as being complementary, in making power measurements, to its existing oscilloscope and probe range. A high proportion of scope users are also power analyser users, the company found, prompting its move to add the product line. Scopes will look at individual functions within a power system; the analyser will monitor end-to-end. You can use the unit to measure for conformance to regulatory standards today and in the future; it has application-specific test modes and a full set of standard features including communication interfaces and PC-based software. Key industries include motor drives, electric propulsion, backup power, alternative energy, and high-efficiency lighting. Many of these engineers work on designs that are subject to government regulations and customer requirements that dictate efficiency and the amount of harmonic distortion or other "line pollution"

The PA4000 handles up to 30A and identifies harmonic components up to the 100th harmonic.

that may be imposed on the power grid. The PA4000 features precisely-matched inputs, wide input ranges and advanced signal processing to deliver consistently high measurement accuracy in all types of measurement environments. A particularly difficult challenge due to the rise of new higher-performance technologies is obtaining consistently high measurement accuracy. The PA4000 uses two Spiral Shunts on each channel – one for current measurements up to 1A, for precise low-current measurements, and one for current measurements up to 30A, for higher-current measurements. This shunt design is then combined with high-speed digital signal processing algorithms, allowing the PA4000 to track power cycles accurately, in the presence of transients and noise

To save engineers setup time and reduce errors, the PA4000 offers a set of application-specific measurement modes such as standby current, motor drive and ballast. The analysers provide LAN, USB, and RS-232 interfaces as well as harmonics measurement capability up to the 100th harmonic. In addition, software for controlling the analyser, downloading measurements, and logging on a PC is also included in the package. The PA4000 Power Analyser has a starting price €8.350.

Tektronix, www.tektronix.com

## USB 2.0 interface, coax physical layer on MOST150 network chip

Microchip has announced a MOST150 Intelligent Network Interface Controller (INIC) with a USB 2.0 high-speed device port and an integrated coax transceiver. According to Rainer Klos, Vice President Systems and Solutions at Micochip AIS, the move brings the multipurpose interface functionality of the USB into the MOST environment, and provides the coaxial cable interface that many car makers are developing for high data-rate traffic. The OS81118 allows you, for example, to create in-car mobile and Wi-Fi connectivity applications on the MOST150 network by connecting a standard Wi-Fi/3G/ LTE module via USB. This solution reflects today's market demands for consumer applications within the automotive environment, such as Internet access, e-mail, social networking and local services. It reflects, Klos says, the prevalence of the USB interface on system-on-chip ICs (SoCs) and ASSPs and supports the trend in the infotainment market to use high-end SoCs, developed for consumer and mobile devices, within automotive applications. However, those SoCs have no automotive-specific interfaces, such as CAN, LIN, MediaLB or MOST; the OS81118 enables automotive engineers to connect up-to-date multi-core consumer SoCs to in-vehicle MOST networks. Besides the optical physical layer (oPHY) interface, the OS81118's coax transceiver opens a cost-reduction path on the MOST physical layer. Additionally, this coaxial physical layer (cPHY) could be used for Advanced Driver Assistance Systems (ADAS). For the developer, the device is a MOST controller that – from the point of view of the traffic and data content – looks like a USB device (both for audio and packet-data traffic): the developer does not need an in-depth knowledge of MOST to use it. Similarly, Klos points out, the operating systems also does not need to know about MOST. You can create a bridge from deeply-embedded functions to a complex OS in an automotive head unit.

The co-ax cable that automotive suppliers are working with is the low-cost 3-mm type similar to that now used as antenna cable, Klos says, "For the next generation [of automotive data rates] you won't get Ethernet over UTP (unshielded twisted pair) [to work in the automotive environment]... STP (shielded) would be required, but co-ax is more effective and cheaper." You can expect bi-directional operation, Klos adds, and you may see power over the same cable. This, he says, suits users who don't want to use optical media: nevertheless, the MOST organisation expedts attention to return to optical fibre for data rates in the 1 – 5 Gbit/sec range, possibly including glass fibre. To enable development and speed time to market, Microchip is also announcing the Physical+ Interface Board OS81118. This board encapsulates the entire physical hardware interface of a MOST network. The Physical+ Interface Board OS81118 comes with a USB 2.0 interface supporting optical and coaxial physical layers, and is expected to be available in Q3/2013. The OS81118 occupies a 72-pin QFN package and will be available for volume production in January 2014.

Microchip; www.microchip.com/get/472T

## MAXIMIZING THE **EFFICIENCY CURVE**

Advanced intermediate bus converters with optional digital interface

## Multi-channel, multi-standard signals to 6 GHz from R&S vector generator

Rohde & Schwarz has introduced the SMW200A high-end vector signal generator that creates complex multichannel scenarios: primarily for communications product development, it incorporates MIMO and fading requirements. High on the list of achievements that R&S claims for the new instrument are the ability to generate a variety of MIMO signal patterns, with fading on all paths. The MW200A high-end vector signal generator creates complex, digitally modulated signals of high quality, with a range of applications that extends from single-path vector signal generator to multichannel MIMO receiver tester. It combines a baseband generator, RF generator and MIMO fading simulator in a single instrument: it can also manage further connected sources as if they were part of the single instrument. The generator covers the frequency range from 100 kHz to 3 GHz or 6 GHz and has an I/Q modulation bandwidth of 160 MHz with internal baseband. Its modulation and RF characteristics suit it to developing high-end components, modules and complete products for wideband communications systems such as LTE-Advanced and WLAN IEEE 802.11ac, and meets the needs of verification of 3G and 4G base stations as well as aerospace and defence applications.

The R&S SMW200A can be equipped

with an optional second RF path for frequencies up to 6 GHz and with a maximum of two baseband and four fading simulator modules, giving two full-featured vector signal generators in a single unit. Fading scenarios such as 2x2 MIMO, 8x2 MIMO for TD-LTE and 2x2 MIMO for LTE-Advanced carrier aggregation can be simulated. Until now, R&S says, this has required complex setups consisting of multiple instruments.

More than two RF sources are required for applications such as 3x3 MIMO for WLAN or 4x4 MIMO for LTE-FDD. In addition to the two internal RF paths provided, R&S SGS100A signal generator modules can be connected as additional RF sources and remotely controlled by the SMW200A. This solution takes up only five height units for 4x4 MIMO receiver tests and provides correctly encoded baseband signals, realtime channel simulation, AWGN generation and, if required, phase-locked coupling of multiple RF paths.

Options for every important digital communications standard are included, and enabled by key-codes: LTE, LTE-Advanced, 3GPP FDD/HSPA/HSPA+, GSM/EDGE/EDGE Evolution, TD-SCDMA, CDMA2000/1xEV-DO and WLAN IEEE 802.11a/b/g/n/ac. The standards run directly, without having to connect an external PC, making

it possible to vary signals or specific parameters quickly and easily. This simplifies troubleshooting on the DUT and also saves time. Because the R&S SMW200A is multichannel-compatible. developers can create scenarios using different signals with minimal effort, for example, in order to test multistandard radio base stations. An R&S spokesman cited this as one of the key differentiating factors that makes the stand-alone instrument - as opposed to the modular, PXI-style - format the optimal choice for this class of test unit. The ease-of-control aspect is shown by the fact that a complete test setup of the SMW200A is memorised by a single command.

High accuracy in spectral and modulation measurements comes from SSB phase noise of -139 dBc (typical) at 1 GHz (20 kHz offset). In modulation quality, EVM is -49 dB (measured) for WLAN IEEE 802.11ac signals; as well as a 0.05 dB (measured) I/Q modulation frequency response over 160 MHz bandwidth. ACLR figures for 3GPP measurements (TM1, 64DPCH) are 73 dB at 5 MHz offset and 75 dB at 10 MHz offset.

A touchscreen allows users to control the instrument intuitively with the Rohde & Schwarz block diagram as key operating element to visualise the signal flow. Touching any parameter opens a keypad to set a value: dragging a connection between two functional blocks (for instance, to apply modulation) creates the connection and sets all relevant parameters. Help functions are provided at all points: presets are provided for all important digital standards and fading scenarios. LTE and UMTS test case wizards simplify complex base station conformance testing in line with the 3GPP specification.

The back panel of the instrument is a module-frame that accepts additional baseband units without requiring calibration of the instrument. R&S comments that one of the achievements of the instrument is to provide in a single box, all of the complex signals, with fading, that previously required a stack of units; compared to the stack that would have been required, the 200A is "half the size, weight and power", the company says.

Rohde & Schwarz, www.rohde-schwarz.com A video is at; www.rohde-schwarz. com/campaigns/en/smw/video.html

The R&S SMW200A can control two further signal sources for complex MIMO pattern generation.

## Single-chip digital radio receivers for consumer electronics

Around 1995, says James Stansberry, VP and General Manager of Broadcast Products at Silicon Labs, CMOS processes achieved an fT (transition frequency) of 25 GHz and this, combined with the development of on-chip passives and the ADC technology to directly digitise RF/IF frequencies, set the scene for CMOS RF ICs of the current generation. Much work since that time has focussed on maximising CMOS' strengths and learning to work around its weaknesses; using digital logic to detect and correct RF and baseband performance deficiencies. You can design for cost, without compromising power or performance, he asserts, using DSP to improve selectivity, give channel equalisation, filtering for noise reduction, and using both digital and analogue techniques. The outcome can be single-chip receivers that represent a massive reduction in component count, size, power and cost over a conventional approach.

Stansberry made these observations in the course of introducing Silabs' Si468xFM digital radio IC, that uses software-defined radio techniques for both DAB/DAB+ and HD Radio for portable and home audio products. Claimed to be the first single-die antenna-input-to-audio-output digital radio receiver solution developed for the global portable and consumer electronics markets and using SDR technology, the monolithic Si468x receiver ICs brings FM, HD Radio and DAB/DAB+ broadcast capabilities to a wide range of audio applications, from price-sensitive clock and tabletop radios to high-end multimedia devices with displays, such as mobile phones, tablets and personal navigation devices.

Stansberry believes that digital radio adoption has been slow, in part due to the high cost of delivering a high-performance yet power-efficient RF solution for the consumer electronics market. The Si468x family provides a single-die solution that reduces system complexity, bill of materials (BOM) count and power consumption without compromising RF performance. Using the company's low-IF digital receiver architecture, the Si468x family claims superior RF performance compared to existing consumer-grade digital radio solutions. The receivers support auto-calibrated digital tuning and FM-seek functionality based on multiple signal quality and band parameters and provide flexible audio processing features including noise blanking, configurable FM soft mute, FM de-emphasis and FM hi-cut filtering. It integrates RF tuner, and baseband and stereo audio DACs. Wafer-level chip-scale packaging (WLCSP) supports very compact designs, enabling a complete digital radio receiver system with only 12 external components to be implemented in less than 100 square millimeters.

Receivers are engineered with small form factor designs in mind. By integrating the RF tuner and baseband functions on a single die, the Si468x family avoids radio self-interference and streamlines system design, validation and testing. Silabs claims the smallest footprint and lowest power consumption of any digital radio solution at less than 60 mW in analogue FM mode and less than 95 mW in HD Radio and DAB/DAB+ modes. Si468x receivers support worldwide analogue FM radio reception and incorporate an integrated decoder for the European Radio Data System (RDS) and North American Radio Broadcast Data System (RBDS) standards including required symbol decoding, block synchronisation, error detection and error correction functions. The Si468x family includes the first truly monolithic digital radio receiver ICs certified by

Worldwide FM and digital broadcast radio reception can be added to a variety of products with low BoM cost.

iBiquity to support the HD Radio standard for portable and consumer electronics applications. The Si468x receiver family is compatible with the European Eureka 147 DAB and DAB+ standards and is designed to be fully compliant with the United Kingdom's Minimum Specifications for DAB and DAB+ Personal and Domestic Digital Radio Receivers. Si468x digital radio receivers come in two package options: a 7 x 7 mm 48-pin QFN package and a 3.2 x 3.8 mm WLCSP package. Pricing begins at \$5.62 (10,000). An evaluation kit is priced at \$550.00.

www.silabs.com/FMtuners

## Battery monitoring technology adds precision for lead-acid chemistry

Texas Instruments has introduced a "gas gauge" IC with an "Impedance Track" function that accurately monitors stateof-health, and state-of-charge of lead-acid batteries used in uninterruptible power supplies and e-bike designs. The first lead-acid battery management gas gauge integrated circuit with TI's proprietary Impedance Track capacity measurement technology, the bq34z110, which comes in a 14-pin package, is the only scalable power management device to support multi-cell lead-acid battery packs with battery voltages of 4V, 12V, 24V, 48V and higher. Lead-acid batteries typically behave better than lithium chemistries in environments with wide temperature ranges. However, today's lead-acid battery designs do not accurately measure and report current battery capacity, which often frustrates the end user, and could mean adding more batteries to keep the system adequately charged. The bg34z110 gauge with Impedance Track technology constantly informs a user about the battery's state-of-health and stateof-charge and maintains up to a 95%-accurate capacity measurement for the entire life of the battery. This information also prevents premature shutdown, increasing the longevity of the battery and end-equipment. The bq34z110 is a multi-cell scalable battery gauge to support a wide range of lead acid batteries (4V to 64V), including large capacity batteries (1 Ahr to 65 Ahr and higher) and high-current applications (0A to 32A and higher). Impedance Track uses current, voltage measurements. temperature and battery characteristics to determine battery state-of-charge, state-of-health and capacity. The chip is supported with application notes, user guide and bg34z110EVM evaluation module.

TI, www.ti.com/bq34z110-pr-eu

www.edn-europe.com EDN Europe | MAY 2013 1

BY HOWARD JOHNSON, PHD

#### **MEASURING NOTHING**

very scope probe picks up extraneous noise. Some of that noise is self-generated, and some may be generated by the system under test. When looking at a noisy, jittery signal, how can you tell which parts of the signal are "real" and which parts derive from noise and interference? There is only one way, and that way, if you embrace it, leads to remarkable insights about noise, grounding, and the nature of digital systems.

The only way to directly observe noise and interference is to attempt to measure nothing. With your probe in place, grounded as it will be for the actual signal measurement, touch the tip of the probe to any nearby point of ground. This configuration is called a null experiment. Ideally, you should see zero, zip, nada, or, as the English call it, "naught." What you actually observe is your own noise floor, a plethora of noise sources, a whole ecosystem of interferences all superimposed. Creative use of your trigger circuits combined with vertical averaging can often pull apart these tiny effects, deeply buried in a sea of foam, for close inspection. You can learn a great deal measuring nothing.

In theory, whatever noise the probe picks up in your null experiment will appear as noise superimposed onto your actual signal, provided the probe is held in a similar physical position. Two main things cause the noise you will see: one, currents flowing on the probe shield due to differences between the electrical potential of the digital logic ground and the scope, and two, interactions between the electromagnetic fields surrounding

the device under test and the probe or probe wiring.

To determine how much noise the former source creates, keep the probe connected to its own ground, but disconnect the probe and probe ground entirely from the device under test. Keep the probe topology otherwise similar to the null experiment. This procedure eliminates the probe-shield currents, leaving only the electromagnetic pickup.

Figure 1 The short signal and ground-attachment pins on this probe pick up little electromagnetic noise.

If probe-shield currents are a serious problem, try a differential probe, with one leg on the signal and the other on digital logic ground. Since both inputs to a differential probe have high impedances—much higher than the impedance of a single-ended probe's ground connection—little shield current will flow during this configuration.

## Every probe picks up extraneous noise.

Regarding the latter source, first determine if the noise is coming from the device under test or something else in the room. With the probe connected to its own ground, but still disconnected from the device under test, pick up the probe and wave it around. Use the probe as a magnetic-field sniffer to locate the culprit. Sometimes a fluorescent light or other circuit may induce noise in this configuration. If so, turn it off.

If electromagnetic noise seems to be coming from the device under test, check the length of the ground attachment between the scope probe and the system. The smaller you make the loop from the signal source, to the probe, and back through the probe's ground connection, the less noise your probe receives (Figure 1). Reduce the size of that loop, and your null-experiment results should improve.

Understanding why this, and a hundred other tricks, works for noise abatement is all part of the art of digital design. If you want to master that art, follow my advice: "Measure not the thing you know; measure naught." EDN

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www. sigcon.com, or e-mail him at howie03@ sigcon.com.

## A SYSTEM-ON-CHIP APPROACH TO INTERFACING STRAIN-GAUGE BASED SENSORS

train gauges are useful sensors to measure the mechanical strain within an object. They are attached using adhesives to the object which is experiencing a force. The resulting change in electrical resistance of the strain gauge element contains information about the applied force. The technique has varied applications of which the most common is weighing scale design, and which include force measurement in various mechanical devices, for example pneumatic valves and civil engineering applications, impact sensors, medical sensors, to name only a few.

With so many applications, strain gauges are useful industrial sensor components. In order to make an accurate measurement of the force applied, understanding the strain gauge and its parameters is important. The sensor signal (change in resistance) needs to be efficiently conditioned so that the resulting signal-to-noise ratio from the system is sufficient to accurately determine the magnitude of stress. (Stress is the force applied to the mechanical structure, that we wish to infer: strain is the resulting deformation.) The measurement system includes an analogue signal conditioning path followed by conversion to digital code. This article begins with an understanding of a strain gauge and proceeds to the various non-idealities one has to be aware while interfacing them. Finally an example of system design for read-out of such sensors is shown using a programmable system-on-chip approach: analogue integration is a practical approach which improves the overall realisation of such an interface circuit for strain gauges.

#### **UNDERSTANDING A STRAIN-GAUGE**

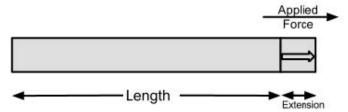

Strain is defined as deformation (within elastic limits) of a body under the application of force. It is a dimensionless quantity and can either be tensile or compressive depending on the surface to which the strain gauge attached.

When a body is under application of a uniaxial force, there is an extension in its length along same direction, as shown in Figure 1. While elongating, it also experiences a perpendicular contraction. This is defined by the Poisson ratio, which is the negative ratio of strain in the perpendicular direction to the strain in the axial direction. Typically a strain gauge has a serpentine/

Figure 1. Concept of Strain

wound pattern in order to maximise the area of the conducting material that comes under the influence of the applied force.

The strain gauge is bonded to the object which is directly exposed to the force. This is known as carrier and transfers the change in physical quantity into a linear change in electrical resistance of the strain gauge. Gauge Factor(G) is used to relate this transformation and is given by:

$$G = \frac{\Delta R / R}{\Delta L / L} = \frac{\Delta R / R}{\varepsilon}$$

The strain-gauge has a nominal resistance which is usually between few tens of  $\Omega$  to few  $k\Omega$ . The first challenge in interfacing the strain-gauge to the electronics is the magnitude of the resistance change. For example, a maximum value of 1m strain together with a gauge factor of 2 gives a resistance change of only 0.2%. This change is very small when we consider the nominal resistance. The typical change can be few  $\Omega$  or much lower. In addition to dealing with such low resistance, there can be many sources of errors during the transfer of force to the resistance change. Ideally the force applied should have a (linear) proportional increase in the resistance. But this is not the case due to the parasitics, for example lead wires from the strain gauge to the circuit can have a larger resistance than the actual change. Also, temperature co-efficients of the straingauge resistance can be crucial as the measurement becomes dependent on another factor. In order to correct for these factors, manufacturers usually compensate for the gauge depending on the temperature co-efficient of the material to which it is attached. This reduces the thermal sensitivity but does not completely eliminate it.

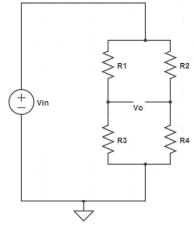

Figure 2. Bridge method to readout resistive sensors

#### **RESISTIVE SENSOR READOUT**

A common method to readout the sensor information is by Wheatstone bridge configuration (Figure 2), in which the imbalance caused by changes in the sensor resistance results in a voltage difference.

The information from the strain gauge is contained in the differential signal (Vo).

$$V_o = \left(\frac{R_4}{R_4 + R_2} - \frac{R_3}{R_3 + R_1}\right) V_{in} \tag{1}$$

One of the simplest measurement methods is to have one resistance of the bridge (R1) replaced by the strain gauge while other resistance of the arm is kept constant, at the nominal resistance of the strain gauge (R3=Rn). This is called the quarter bridge method. R2 and R4 are held at the same magnitude resistance.

$$R_1 = R_n (1 + \varepsilon G) \Omega \tag{2}$$

Using the above assumptions in (1) gives us:

$$V_o = \frac{\varepsilon G}{4} \left( \frac{1}{1 + \frac{\varepsilon G}{2}} \right) V_{in}$$

(3)

One additional modification to the quarter-bridge circuit is to add a very accurate shunt resistance across the bridge, which can be used to calibrate the arrangement. (Finding the voltage difference with shunt resistance, and without shunt resistance, will give a measure of voltage change per  $\Omega$  change).

As seen from equation 3, the output voltage depends on a non-linear term. In order to remove this, we can modify the bridge to include – instead of R3 – a dummy strain gauge perpendicular to the applied force. This gauge is affected by temperature in same way as the measuring element but is not affected by the sensing quantity.

Going one step forward, we can have an active gauge which is affected in the opposite direction (compress as against elongate), thus making the output linearly dependent with twice the sensitivity as given by equation 4. This is known as half-bridge method.

$$V_o = \frac{G\varepsilon}{2} \tag{4}$$

An extension of the same principle is including active elements in each resistance, with each arm having gauges affected by increase and decrease of the applied force. This is also known as the full-bridge method, and involves using four strain gauges and results in the most sensitive response in terms of magnitude.

$$V_o = G\varepsilon$$

(5)

When using a full bridge, maximising circuit sensitivity is achieved by including two gauges in transverse direction with two in the axial direction of measurement of force. It should be noted that using four bridges does not increase circuit sensitivity. Therefore it is not economical to use four gauges; instead two gauges should be connected in series for one quarter of bridge.

#### SOURCES OF ERROR

Firstly in all the previous analysis, we assumed ideal components. In real-world applications, tolerances on the resistances come into effect. These result in saturation of voltage as well as a large common-mode offset since the actual resistance change in the bridge is small. Techniques such as offset-cancellation using auto-zeroing or modification to include a balancing circuit to adjust for the tolerances by means of trimming or calibration can overcome this problem.

The second error is due to the wire resistance which connects the gauge to the bridge, which desensitises the strain gauge measurements. As seen in equation 6, this results in a modified gauge factor which should be used for correction when calculating the effective force applied. This additional resistance causes offset and gain errors: dependence of lead-wire resistance on temperature is an additional source of error.

$$\frac{\Delta R_1}{R_1} = \frac{\Delta R_g}{R_g + 2R_L} = \frac{\varepsilon G}{1 + 2\frac{R_L}{R_g}} = \varepsilon G^*$$

(6)

The bridge is strapped on to the surface of the object to monitor the applied force. The lead wire introduces additional resistance as well as acting as source of noise pick-up. Including these in a quarter bridge-configurations gives us the output voltage as:

$$V_o = \frac{1}{2}A\left(\frac{1}{1+\frac{1}{A}}\right) \tag{7}$$

Where factor A is given by

$$A = \frac{\varepsilon G}{2} + \frac{R_L}{R_n}$$

(8)

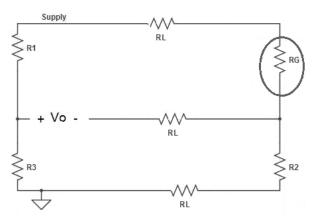

The lead-wire resistance is overcome by using a three-wire connection. Consider the three wire bridge circuit shown in Figure 3. RL indicates the wire resistance while supply (VS) is the excitation voltage to the bridge. Considering R1, R3 to be equal

$$R_{G} = \frac{R_{2}(V_{S} - 2V_{O}) - 4V_{O}R_{L}}{V_{S} + 2V_{O}}$$

Figure 3: Three wire connection to the strain-gauge

The middle resistance through which no current flows, acts as a sense lead. The assumption in order to have complete compensation is that the lead resistances are the same, have the same temperature coefficients and are maintained at same temperature. In reality this is not true and hence other complex schemes such as four-wire or offset compensation mechanisms are used.

#### INTERFACE CIRCUIT DESIGN

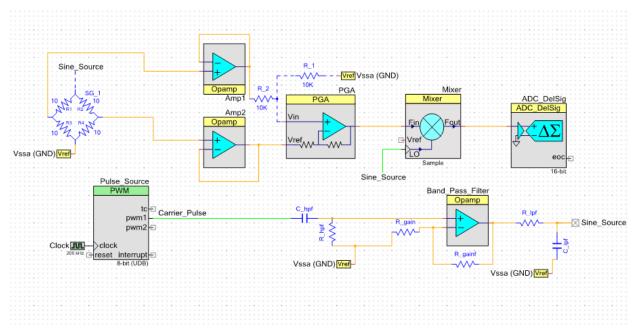

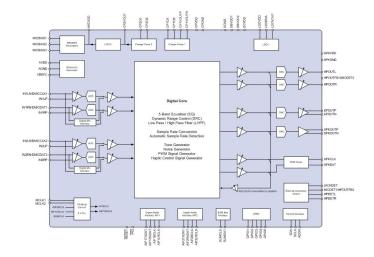

In this section, we discuss a possible interface circuit for straingauge; in this implementation, the complete design apart from the bridge itself can be encapsulated in one of Cypress' Programmable System-on-Chip (PSoC 3) devices. The overall design is shown in Figure 4. The configuration we use here is a modulation scheme in which a sinusoidal signal is used.

The PWM generator is used to feed the source excitation signal through a bandpass filter with centre frequency of 5 kHz, to the bridge. An active bandpass filter is realised using the available opamps within the PSoC. The components identified as C\_hpf and R\_hpf control the high-pass filter response while

R\_gain and R\_gainf provide the gain, and where R\_lpf and C\_lpf provide the low-pass filtering. A cascade of these configurations provide the required bandpass behaviour which filters the sinusoid from the PWM generator, to be fed to the bridge as excitation source. The signal is then amplified by the instrumentation amplifier, which uses the three-opamp topology, before being down-converted using the mixer and the same sinusoidal signal source. The down-converted signal which contains the sensor information (difference in node voltages) is digitised by a  $\Sigma\Delta$  converter. The  $\Sigma\Delta$  converter can have up to 20-bits of resolution based on the sample rate required from the read-out channel.

The strain gauge is a useful sensor in industrial applications, given that its principle of operation is understood and its various forms of errors are taken into account. This article has shown a method of interface circuitry using carrier frequency excitation of the bridge. The complete design can be implemented on-chip using Cypress' PSoC which increases the performance and provides the required accuracy in such interface applications.

#### **REFERENCES:**

- 1. "PSoC3 Architecture TRM", Cypress Semiconductors Corp.

- 2. "Strain gauge selection (TN-505)", Vishay precision group.

- 3. Wendladt et al., "Signal conditioning for resistive strain gauge sensors in mobile applications", SomSed Workshop, TU Hamburg, 2009.

#### ABOUT THE AUTHOR

Umanath Kamath is currently a Senior Design Engineer with Cypress Semiconductor. He received his Masters degree in 2012 from Delft University of Technology, Delft, the Netherlands and Bachelors degree in 2009 from M.S.Ramaiah Institute of Technology, Bangalore, India both in electronics. He has held visiting positions during his studies with IMEC and CMOSIS in Belgium and Honeywell Research Labs in India. He can be reached at umrk[at]cypress[dot]com

15

Figure 4. Example of an interface circuit for strain-gauge sensor using Programmable System-on-Chip

EMBEDDED-SYSTEM ARCHITECTURES

BUILT ON A COMBINATION OF

MCUS AND FPGAS OFFER THE KIND

OF ADAPTABILITY INCREASINGLY

REQUIRED TO SUPPORT

CHANGING DEMAND FOR GREATER

FUNCTIONALITY ACROSS DIVERSE

APPLICATIONS.

BY MICHAEL PARKER • ALTERA CORP

ith the integration of dual ARM A9 CPU cores, a complete set of ARM peripherals, the ability to implement in hardware either fixed or floating-point signal processing, and unmatched I/O flexibility, the

latest FPGA system-on-chip devices can perform what used to require a complete circuit card containing dozens of chips. A perfect example is next-generation motor control.

Next-generation motor-control systems are designed to deliver maximum motor efficiency using very fast control loops that exceed the capabilities of processor-only solutions. The inner control loops, implementing what is known as field-oriented control (FOC), require transforms best performed in floating point. FPGA SoCs that combine dual processor cores and FPGA fabric are ideal for this application, combining in a single device the capabilities of general-purpose processors and high-performance logic for specialized algorithms (see sidebar "How FPGAs and multicore CPUs are changing embedded design").

#### MOTOR COMMUTATION

Electric motors rely on basic electromagnetic principles. Forces due to magnetic attraction and repulsion are used to generate torque, as well as the resulting rotary motion of the motor.

Magnetic fields are generated in both the rotor and the stator, through the use of either permanent magnets or electromagnets. Proper alignment of the magnetic fields as the rotor turns is required.

The magnetic fields must continuously change to maintain an alignment that produces torque throughout the rotor's full 360 degrees of rotation. This process is called commutation. The most basic method used is the dc brush motor. This motor design has permanent magnets in the stator and one or more electromagnet pairs in the rotor. In order to eliminate the sparking and wear of brushes for mechanical commutation, the motor design can be turned inside out by placing the permanent magnets on the rotor, and the electromagnets in the stator. Replacing mechanical with electronic commutation can achieve the same effect, and is known as a brushless dc motor.

#### FIELD-ORIENTED CONTROL

In a dc brush motor, the control loops can simply drive the motor current variable, and the brushes perform the mechanical commutation function, although in a suboptimal fashion. With FOC, sinusoidal commutation will be performed electronically in an optimal fashion, using integrated control loops to maximize the magnetic field compo-

#### AT A GLANCE

- Given the rapid growth of new standards and protocols as well as increasing pressure to speed time to market, embedded-system design is due for a disruptive paradigm change.

- The latest FPGA system-on-chip devices can perform what used to require a complete circuit card containing dozens of chips.

- SoC FPGAs for real-time applications such as motor control provide both integration benefits and the ability to scale performance.

nents producing useful torque and minimize magnetic field components that do not yield torque (perhaps, for example, merely exerting force on the motor bearings). The object of FOC is to ensure the magnetic fields are precisely orientated at all times to produce maximum torque, eliminate torque ripple, and thereby increase motor efficiency and lower the cost of ownership of the system.

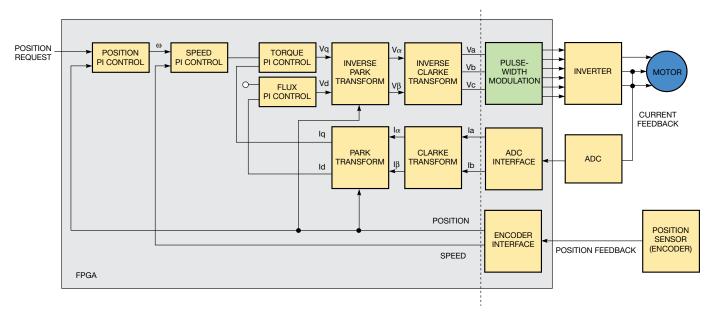

The FOC function shown in **Figure 1** uses Park and Clarke transforms as well as PI control loops for torque (useful oriented magnetic field direction) and flux (magnetic field direction producing no torque). PI controllers are used rather than the PID controllers typically seen in control systems. (The derivative term is not used.)

Motors normally use three independent phases. These phases can be replicated around the stator, giving the number of poles or windings. In a three-phase system, the sum of the currents is defined as zero by Kirchhoff's law.

This means that a three-phase current vector (a, b, and c components) can be expressed as two orthogonal phases ( $\alpha$ ,  $\beta$  components), using the Clarke transform. The Clarke transform is valid at a given rotation angle of the rotor.

Using the Park transform, these current vectors are mapped onto the rotating plane of the spinning motor. This results in the  $\alpha$ ,  $\beta$  components being mapped into q (quadrature) and d (direct) components. The transform requires the rotor angle, which is the input, often determined by a quadrature encoder attached to the rotor shaft. The Clarke and Park transforms, therefore, need to be continuously calculated as the motor rotates.

#### **REQUIREMENTS**

While motor-control applications are mechanical, the rate at which the drive circuits must be updated and the current, position, and speed sensors read can be quite high. A reasonable scenario might be a motor operating at a maximum of 12,000 RPM, or 200 revolutions per second (RPS). If we use a rule of thumb that a minimum of 80 samples is needed to generate a well-shaped sinusoidal current waveform, then the required sample rate will be the equal to motor speed (RPS) × 80 × number of motor pole pairs.

The number of motor pole pairs is the number of electromagnetic windings in the stator. For a motor at 12,000 RPM with eight windings or pole pairs, this works out to a sampling rate of 128,000 per second, and a processing latency of

Figure 1 This FOC-based motor-control system uses Park and Clarke transforms as well as PI control loops for torque and flux.

### HOW FPGAs AND MULTICORE CPUs ARE CHANGING EMBEDDED DESIGN

#### BY SANJAY CHALLA, NATIONAL INSTRUMENTS

With the explosion of embedded devices in the past few decades, many improvements have been made in both the hardware components and software tools. Despite this innovation and growth, however, traditional embedded-system design approaches have evolved little if at all and are increasingly proving to be a hurdle. Given the increasingly rapid growth of new standards and protocols as well as increasing pressure on design teams to deliver to market more quickly, embedded-system design is due for a disruptive paradigm change.

With the accelerating growth of advances in hardware technologies and software tools, the challenge posed by integration is set to rise. This challenge, if unaddressed, will result in more expensive end products and can prevent experimentation, growth, and delivery of more innovative designs to the

marketplace.

#### STANDARD EMBED-DED ARCHITECTURE

In the general computing marketplace, standardization has resulted in more robust operating systems, more refined end applications, and advances in the underlying hardware components. The lesson learned is that time saved in avoiding the integration effort of custom hardware architectures and associated software components results in better end solutions, which are delivered to market faster.

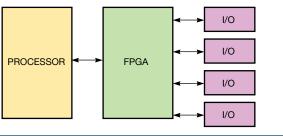

For the embedded space, a corresponding standard architecture needs to be flexible enough to adapt to diverse use cases while providing an avenue for updates. Given these constraints, the most robust architecture for standardization in the embedded design space is a microprocessor and an FPGA working alongside each other

as a single unit (Figure A).

Together, these two elements

enable substantial flexibility

in designs.

FPGAs offer the benefits of hardware determinism and reliability without the up-front cost and rigidity of ASIC design. Additionally, the ability to load new logic and redefine the connections in the FPGA fabric makes it possible for designers to future-proof designs and benefit from more robust updates without requiring any substantial modifications to hardware.

The combination of processors and FPGAs in embedded-system design is growing in many industries. Embedded-systems developers are using designs based on several processors and FPGAs. The FPGAs are used to take accurate, high-speed measurements or run time-critical algorithms. Meanwhile, the processors run a real-time operating system to handle lower-frequency control loops or provide Ethernet communication to other distributed nodes and facilitate remote data access, system management, and diagnostics.

Figure A In this standard hardware architecture, the combination of a processor and an FPGA enables flexibility while making it possible for standardization that can utilize higher-level tools to make substantial gains in the design workflow. The processor makes it possible to reuse existing code libraries, while the FPGA allows for the flexible implementation of custom algorithms.

#### HIGHER-LEVEL TOOLS

A key benefit of a standard architecture is that more capable and optimized highlevel tools can be developed and used for design. Higherlevel tools make it possible for domain experts to be more closely involved in embedded-system design with smaller and more efficient design teams. As a result, more complex products can be pushed to market sooner with smaller design teams.

General-purpose computing provides evidence for the efficiencies that can be gained in application development with higher-level design tools and languages. Unsurprisingly, the embedded marketplace has started to witness the growth of higher-level design tools, including the Xilinx AutoESL C-to-Gates high-level synthesis tool, Mentor Graphics Catapult C Synthesis tool, and NI LabVIEW ultimate system-design software.

#### **AUTHOR'S BIOGRAPHY**

Sanjay Challa is a product manager for embedded software at National Instruments, with a focus on real-time operating systems and FPGA-based embedded systems. He joined the company in 2010. Challa received his bachelor's degree in biomedical engineering from the Georgia Institute of Technology (Atlanta).

#### 7.8 µsec.

Each application will be different, but often the system must be designed such that it can acknowledge and process all interrupts and update the motor drivers within 5 µsec or less. The process is to sample the feedback motor currents, position, and speed, and use FOC to calculate updated motor current driver values at a rate of 200,000 per second with a 5-µsec processing latency. For a

processor-based system, this implies an interrupt rate of 200 kHz, which can be a significant challenge for general-purpose processors with caches, operating systems, and non-vectored interrupt controllers.

#### PROCESSING SYSTEM

Use of an SoC FPGA system can allow a more optimal and flexible implementation. The SoC contains two 800-MHz ARM

Cortex A9 microprocessor systems.

The ARM A9 processor is a more general-purpose, high-performance processor, but it is not optimized for demanding real-time applications with guaranteed response times. Real-time performance limitations can be mitigated, however, by taking advantage of the integrated programmable logic of the SoC FPGAs. The programmable logic can be used for PWM drive circuits,

19

www.edn-europe.com EDN Europe | MAY 2013

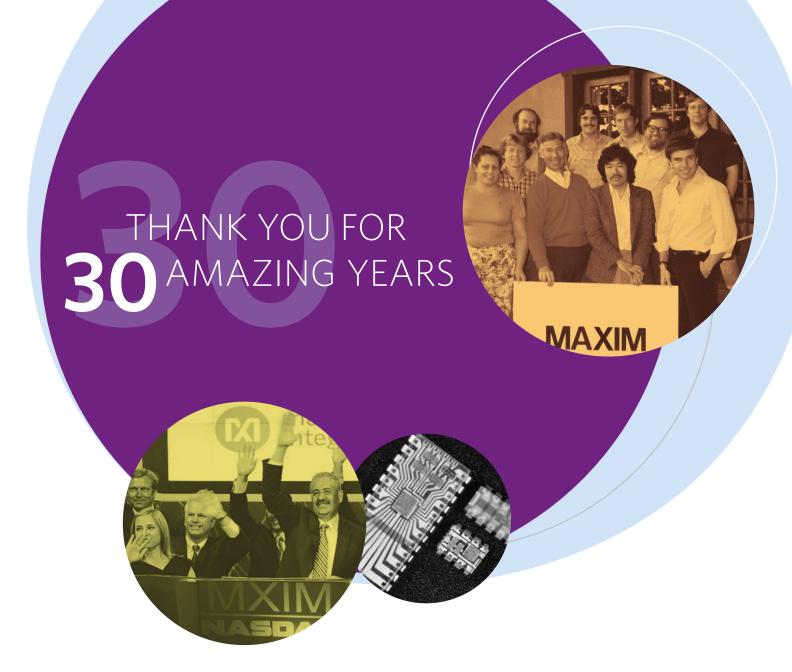

| TABLE 1 HARDWARE RESOURCES TO IMPLEMENT IN SOC FPGA (5CSEA2)   |                   |                               |                    |                                      |  |  |

|----------------------------------------------------------------|-------------------|-------------------------------|--------------------|--------------------------------------|--|--|

| FPGA hardware resources and performance                        | Logic<br>elements | Variable precision DSP blocks | M10K memory blocks | F <sub>MAX</sub> /processing latency |  |  |

| Floating-point FOC, including Park, Clarke, and PI controllers | 7.7K              | 2                             | 1                  | 120 MHz                              |  |  |

| Available resources                                            | 25K               | 36                            | 140                | 1.74 µSEC                            |  |  |

| 5CSEA2 SoC FPGA (%)                                            | 31                | 5.5                           | 0.7                |                                      |  |  |

versatile interfaces to any ADCs and DACs, position and speed sensor interfaces, safety cut-off circuits, a proprietary network or MAC hardware interface, and more. It can also implement the FOC and control loops with less latency and much faster response time than are possible using processor-only systems. Typical system response time is less than 2 µsec, which is about an order of magnitude faster than most processor-only systems can support.

#### **FOC HARDWARE**

A design tool such as DSP Builder from Altera can be used to take a Simulink representation of a design and implement it directly into FPGA logic. DSP Builder also generates floating-point logic, just like the simulation, to provide greater dynamic range and numerical stability than fixed-point implementations allow. The resources used to implement in the smallest SoC FPGA are shown in **Table 1.**

All interfaces to the FOC blocks are memory mapped by Altera's DSP Builder and Qsys tools into the ARM processor system. This allows for software control of the desired torque output, for the gains of the PI loops controlling torque and flux, for monitoring operations, and for other functions.

#### **CONTROL-LOOP HARDWARE**

The position and speed control loops may also be implemented in logic, similar to the PI control used in the FOC function. The gain stages of the different PID circuits can be updated using memory-mapped registers to the ARM processor. If needed, this can provide extremely low latency and fast response at the same rate as the commutation function. Sub-5-usec total response of the control and FOC is easily achievable, which can provide more stability for very-fast-reacting systems. Just as in FOC, these control loops can be implemented in hardware from Simulink models, using DSP Builder to provide floating-point hardware in the FPGA loaic.

Another consideration is that multiple axes of motor control can usually be added to the FOC hardware with a small increase in logic size and processing latency. A four-axis motor controller may

have 20% higher logic use and minimal latency increase over a single-axis implementation. In a software-based implementation, the latency will scale in a roughly linear fashion.

#### **CONTROL-LOOP SOFTWARE**

Motor control loops are most commonly implemented in software using C code. Due to the effect of the FOC's isolating the control loops from the motor commutation, the interrupt rates and latencies of the motor control can be determined by the response of the system, which is normally much slower than the PWM commutation circuits. Simulation and analysis are required to determine the minimum update rates for expected performance and stability; however, an update rate of 10 kHz is normally adequate. In this case, the torque settings to the FOC would be updated at this lower rate (every 100 µsec), based upon feedback and calculation of the current position and speed information.

This SoC approach allows for the hardware to be used for the FOC "inner loop" and the ARM A9 for the motor control "outer loop." The inner loop can guarantee latency under 2 µsec in the FPGA hardware. The ARM can achieve very reasonable processing latency under most conditions and is ideal for outer-loop processing where interrupt latency requirements are much more re-

laxed, and the consequences of missing an interrupt are not catastrophic.

#### **ARM A9 INTERRUPT LATENCY**

The following is based on an analysis by the Altera SoC engineering team of real-time system performance of the ARM processors contained in low-cost SoC FPGAs, specifically interrupt latency. Interrupt response time can vary with system configuration, operating systems, cache configuration, and processing-task load.

The team considered the following scenarios:

- Stage 1: Highly constrained system on a single core to establish a benchmark for the lowest latency that can be achieved (To measure the maximum achievable performance, this stage did not use an OS, and the tests are implemented using bare-metal drivers.)

- Stage 2: Similar to stage 1, but the tests are implemented using an RTOS (µC/OS-II) and the measurements are repeated over a number of iterations (1024) to get a statistical model of the interrupt latency

- Stage 3: Similar to stage 2, with multiple background tasks running on the RTOS alongside interrupt latency measurements (This background task writes data onto the UART port in an infinite loop, and in addition, another background task is performing memcpy in the external

| TABLE 2 MEASURED INTERRUPT RESPONSE LATENCY (MSEC) |         |         |         |         |  |

|----------------------------------------------------|---------|---------|---------|---------|--|

| Cache configuration                                | Stage 1 | Stage 2 | Stage 3 | Stage 4 |  |

| Cache disabled                                     | 2.53    | 2.65    | 2.87    | 2.89    |  |

| L2 enabled                                         | 0.57    | 0.54    | 3.53    | 1.5     |  |

| L1 enabled                                         | 0.16    | 0.19    | 1.29    | 1.29    |  |

| L1 and L2 enabled                                  | 0.16    | 0.19    | 1.28    | 1.3     |  |

| TABLE 3 MEASURED FOC LATENCY (μSEC) |                                 |                |                  |  |  |

|-------------------------------------|---------------------------------|----------------|------------------|--|--|

| Cache configuration                 | Interrupt response<br>(stage 4) | FOC processing | Total<br>latency |  |  |

| L2 enabled                          | 1.5                             | 3.27           | 4.77             |  |  |

| L1 enabled                          | 1.29                            | 0.83           | 2.12             |  |  |

| L1 and L2 enabled                   | 1.3                             | 0.73           | 2.03             |  |  |

memory in an infinite loop, which generates AXI read/writes that may require a long time to complete.)

• Stage 4: Emulation of a larger system where not all code can fit within the L1 cache (In this case, the critical code is placed in the L2 cache. Since the cache is likely to be large enough to hold the whole of the background processing code, after each interrupt, L1 cache flush is triggered. The objective here is to measure the interrupt latency achievable when using the SoC FPGA with a real-time operating system in a real-world environment where cache flushes play a significant role in system performance.)

Cache (L1 & L2) has the most influence on the interrupt latency (Table 2). In a stage 4 situation, with the instruction code locked in L2, the latency is significantly lower than the same system running from external memory. With L1 enabled, it is lower still. The latency will be much worse in the stage 3 and 4 cases, however, due to the background tasks that cause the ISR code to be replaced with other background tasks.

The interrupt response latency needs to be added to the processing time of the FOC **(Table 3).** A basic FOC algorithm was benchmarked, including trigonometric functions, Clarke/Park transforms, PID controller, and inverse Park/Clarke transforms.

Due to the processor performance of the ARM A9, a software-based FOC controller has been shown to be able to meet the 5-µsec requirement. There is little margin, however, and interrupt response times are often the most nondeterministic part of the system. While the results shown are the longest latencies seen under these test conditions, much longer times may occur on occasion, due to the statistical nature of the processing-task load. However, in the case where interrupts are occurring at rates on the order of 10 to 20 kHz, or 50 to 100 µsec, it appears that the ARM Cortex A9 can meet the real-time requirements with extremely high margins, and very low probability of not servicing interrupts in a timely manner. By isolating the ARM interrupts from the much higher-speed FOC commutation requirements, real-time performance is virtually assured under a wide variety of operatin-bobg conditions and processing loads.

The use of SoC FPGAs for real-time applications such as motor control provides not only integration benefits but also the ability to scale performance as needed. This approach allows high-rate, deterministic functions (inner loop) to be implemented in hardware, while lower-rate, more dynamic and complex processing (outer loop) can take place in software, providing the best of both worlds to the system designer.**EDN**

THE USE OF SOC FPGAS FOR REAL-TIME APPLICATIONS SUCH AS MOTOR CONTROL PROVIDES NOT ONLY INTEGRATION BENEFITS BUT ALSO THE ABILITY TO SCALE PERFORMANCE AS NEEDED.

#### **AUTHOR'S BIOGRAPHY**

Michael Parker is principal architect for DSP product planning at Altera Corp. He joined the company in January 2007 and has more than 20 years of DSP wireless engineering design experience with Alvarion, Soma Networks, TCSI, Stanford Telecom, and numerous start-up companies. Parker holds a master's degree in electrical engineering from Santa Clara University (Santa Clara, CA) and a bachelor's degree in electrical engineering from Rensselaer Polytechnic Institute (Troy, NY)

## Your Global Link to the Electronics World

#### www.edn-europe.com

#### www.electronics-eetimes.com

#### www.microwave-eetimes.com

www.eetsearch.com

www.edn-europe.com EDN Europe | MAY 2013 2

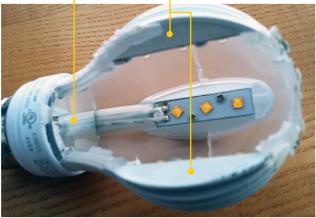

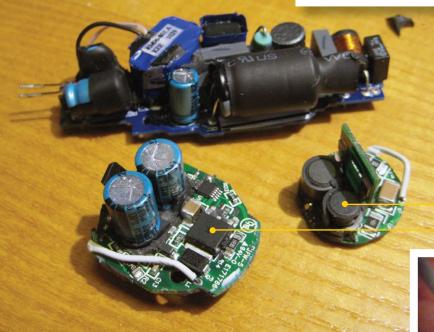

### LED light shrinks size, cost with nonisolated driver

ED-bulb prices are dropping. A year ago you could expect to pay \$50 for a Philips dimmable 60W-replacement LED bulb, while today you can go to Best Buy and purchase its house-brand 8W, 800 lumens Insignia 60W-replacement bulb for just \$17. What has changed in LED-bulb design to allow this price drop? Tearing apart the bulb gives us a look into some design trends in LED lighting, such as how the LEDs are

placed within the bulb and what driver architecture is used.

The Insignia bulb has a shape similar to the familiar incandescent light, with the addition of three metal heatsink fins and a plastic bulb instead of glass.

The plastic bulb cover was removed with a Dremel tool, exposing the six Cree white LEDs that illuminate the bulb's light-mixing chamber, which allows an even glow with no pixelation. The metal fins on which the LEDs are mounted serve both to elevate the LEDs and as heat sinks. At the bottom of the mixing chamber is a paper-thin aluminum reflector that helps reflect the light up and out of the bulb. All of the electronics for this bulb lie beneath the mirror in the base of the bulb, in a separate and encapsulated compartment.

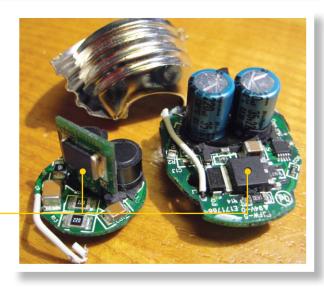

Removing the rubbery potting compound shows that the electronics are mounted on two PCBs that nestle together. Here, the PCBs are separated and next to the bulb's base.

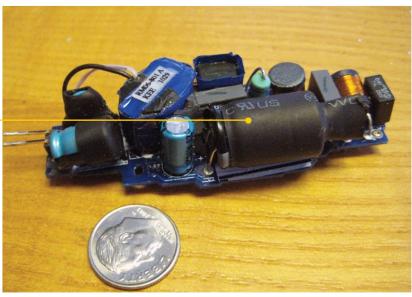

For comparison purposes, the driver electronics are shown for an LED-light teardown from about a year ago. Not only is the packaging quite different, but also there are a lot more electronics. For example, the older design has three electrolytic capacitors and a very large transformer.

The two different generations of drivers are shown side by side:

The Insignia driver has just two relatively small e-caps. This setup raises the question: What LED-driver IC does the bulb use, and how does it allow such a tiny driver?

Question answered: The "SUL B" on the tiny IC is the marking for the Texas Instruments LM3445. There is no transformer, indicating that the LED-driver design is nonisolated. The incandescent-bulb design itself is nonisolated. If you broke the glass in an incandescent bulb while it was plugged in, you would have direct access to the ac-line power. Clearly, nonisolated designs can be made fully compliant with UL specifications. Note: While a nonisolated ac/dc LED-driver design can both be safe and meet UL specifications, developing and testing a nonisolated offline LED driver in the lab requires stringent lab-safety procedures.

Dimming is an important bulb characteristic for the US market. I used a Lutron Maestro dimming switch, with a programmable dimming control, and did a side-by-side comparison with an incandescent bulb. The Insignia dimmed consistently and smoothly, with a dimming profile similar to the incandescent bulb.

Watch a video of the dimming test at http://bit.ly/145ROBK.

www.edn-europe.com EDN Europe | MAY 2013 23

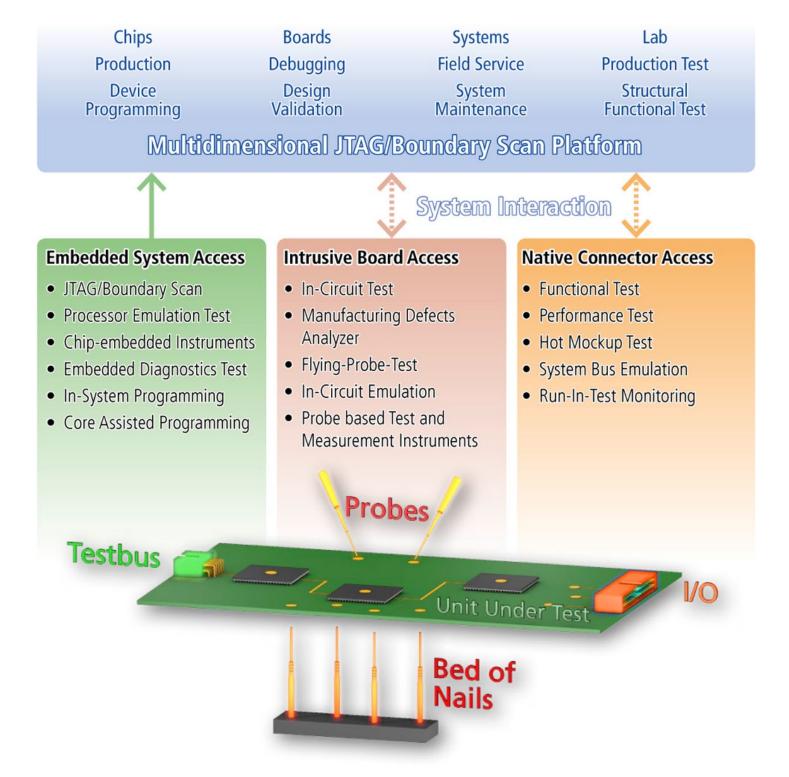

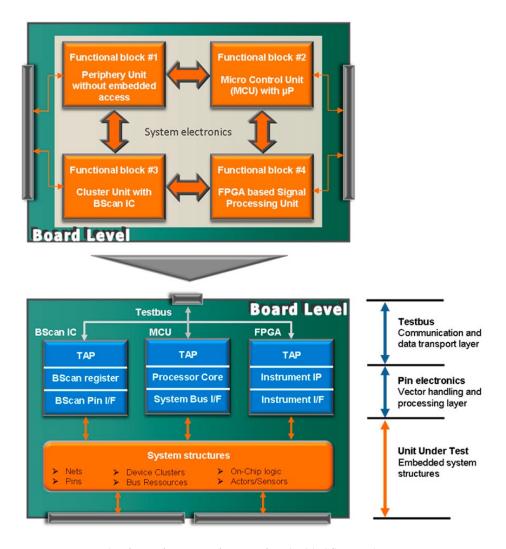

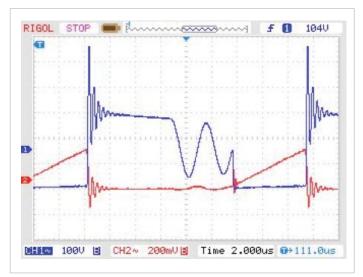

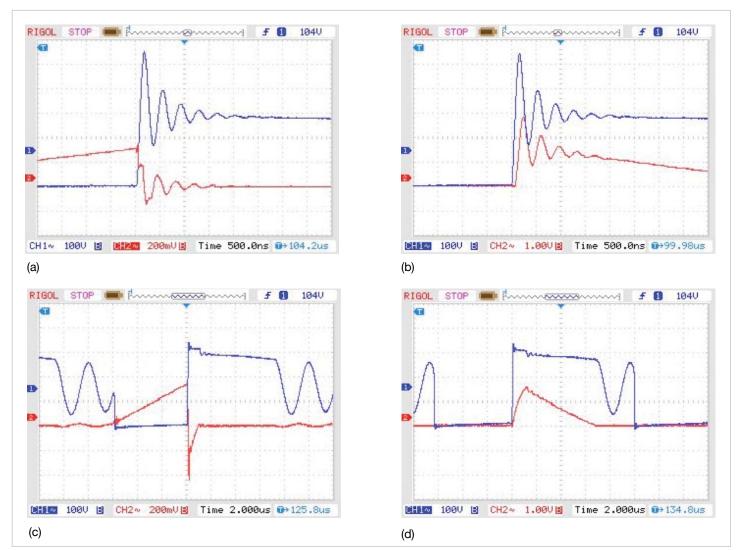

## TEST & MEASUREMENT TECHNOLOGY GOES EMBEDDED

he term "embedded" can be found in nearly every development sector. And everybody is working to broaden the embedded factor, be it on the chip or board level. In particular, the high rate of innovation occurring in microcontrollers and FPGAs enables opportunities for creation of multifunctional electronics, that are more intelligent, more suitable for networking, re-configurable, and compact in size. New 3D chip technologies will boost this trend as the hunger for smart solutions in sectors such as cars, consumer electronics, aerospace, and industrial electronics is insatiable.

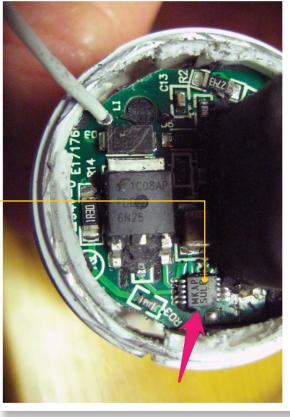

Successful development of such highly complex products requires excellent command of software design, FPGA design, and board design. No less important are excellent skills in coordination of all distinct stages of development, from design concept to final prototype validation. In this context the so-called "V-model" plays an important role (see Figure 1).

The V-model defines adequate verification procedures for every design step to ensure a structured final overall validation. Throughout the current model, structured process steps have complemented pure functional considerations. This is due to the fact that structured validation and tests, as elements of a design-for-testability strategy, have become standard in modern design and production test environments, and their importance is still increasing.

To be able to meet the requirements

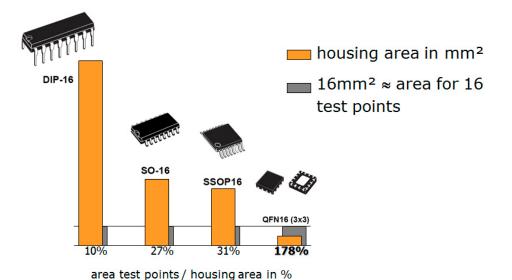

test probing of signals can, today, only partly serve as a developer's means of accessing the required signal information. Test engineers suffer from the same experience when it comes to the use of traditional in-circuit-test strategies in production. Here miniaturisation in electronics leads to problems: reduced test coverage, tremendously increased costs of fault-finding, and, finally, the feared 'no-failure-found' syndrome.

Common suffering, however, sometimes leads to completely different reactions. Some people start to haggle over every test point for every new design, others switch to using using flying probe testers (which are capable of contacting very small areas down to pin lands), and still others look to improved functional tests as the only way forward. However, the reality is that neither in-circuit-tests nor flying probers can really help to solve the validation problem. And test

points are disappearing. So, the need for an alternate strategy is really urgent here. But if access is possible, It might be thought that all this discussion should no longer be necessary.

#### THE ART OF MEANINGFUL SEEING

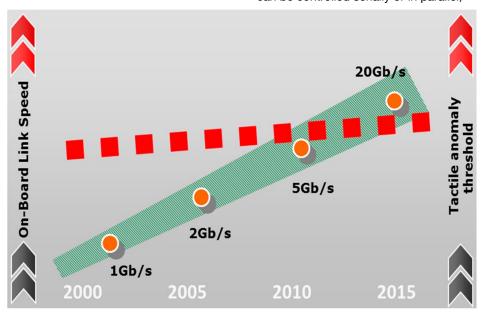

To transmit and process information faster, you need to increase the speed of internal signal flow. In addition to the transition to parallel processing using multi-core systems, an additional trend is increased signal transmission rate. This is especially important in the changeover to serial Gigabit links. Externally, such Gigabit connections are implemented using standard communication buses such as USB3.0, PCI Express, or SATA Express. For instance, they are increasingly used as a high-speed transmission medium for chip-to-chip communication on board.

One of the top drivers of innovation is FPGA technology. The latest generations of FPGA devices from Xilinx or Altera offer fantastic transmission rates of up to 28 Gbit/sec – in parallel on up to 96 channels. However, the design-in process of such Gigabit links requires great care. Due to the high frequencies involved, these connections are bound up with the typical challenges of analogue technology, though differential transmission technology relieves some of the pressure.

Design rules are extremely stringent and require an impedance-matched implementation to ensure the highest quality of signal transmission. High-quality Gigabit analysers with special test probes are available to validate such connections. Nevertheless, probing of Gigabit signals will always affect signal integrity. It's like the task of touching a glassy water surface without generating waves; at best, the waves might be

Figure 1 Definition of hierarchically structured development and verification

Our world changes by the nanosecond. New connections are formed. Old problems are solved. And what once seemed impossible is suddenly possible. You're doing amazing things with technology, and we're excited to be a part of it.

#### www.maximintegrated.com

Figure 2 The required board area for test points is getting more critical

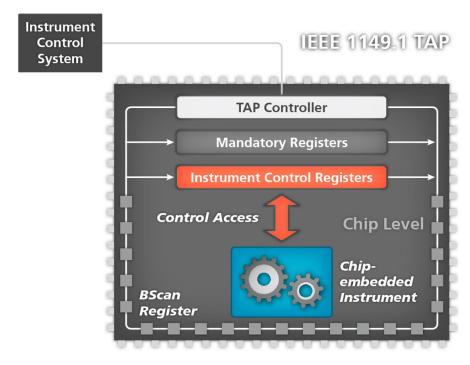

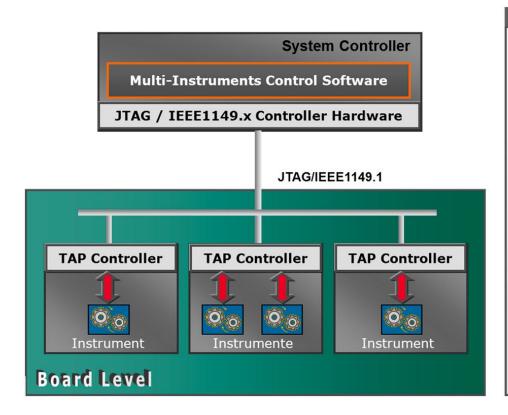

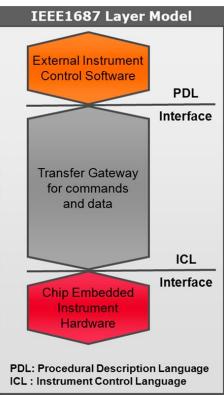

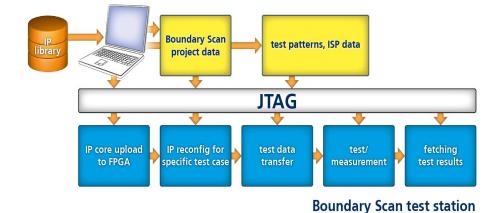

minimised.